数字集成电路版图设计(二) 基于Cadence IC的简单反相器版图设计实践

在数字集成电路设计流程中,版图设计是将逻辑电路转化为物理实现的关键一步。反相器作为数字电路中最基本、最核心的单元,其版图设计是初学者掌握版图设计理念与工具的绝佳起点。本文将介绍如何使用业界主流的Cadence IC设计工具,完成一个简单反相器的版图设计。

一、设计准备与目标

在开始设计前,需明确设计目标:采用特定工艺(例如某180nm CMOS工艺),设计一个驱动能力适中的标准反相器。其原理图通常由一个PMOS管和一个NMOS管组成,输入端共用,输出端连接两管的漏极。我们需要在版图设计中实现这一电气连接,并满足工艺设计规则(Design Rules),确保最终的可制造性和可靠性。

二、Cadence IC环境启动与单元创建

- 启动Cadence Virtuoso,并建立或载入相应工艺的设计库(Technology Library)。

- 在库管理器中,创建一个新的版图单元视图(Layout Cell View),命名为“INV”。

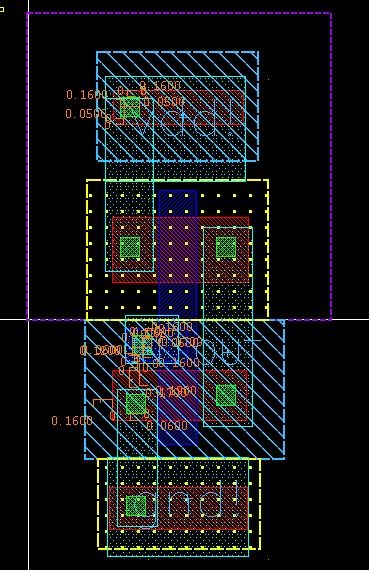

三、版图绘制核心步骤

- 绘制有源区(Active Area):在版图编辑窗口,选择“Active”或“Diffusion”层,分别绘制PMOS和NMOS晶体管所需的有源区矩形。两者之间需保持足够的间距以满足设计规则。

- 绘制多晶硅栅极(Poly Gate):选择“Poly”层,绘制一个横跨PMOS和NMOS有源区的长条形矩形,形成反相器的公共输入端(栅极)。多晶硅与有源区相交的部分即定义了晶体管的沟道区域。

- 绘制选择层(Select/Implant):分别绘制P型选择层(P-Select)覆盖PMOS有源区,以及N型选择层(N-Select)覆盖NMOS有源区,以定义阱内掺杂类型,从而区分PMOS和NMOS。

- 绘制接触孔与金属连线:

- 电源与地:在PMOS有源区上端,通过“Contact”或“Via”层绘制接触孔,并用第一层金属(Metal1)连接到VDD电源线。在NMOS有源区下端,同样绘制接触孔并用Metal1连接到VSS(地)线。

- 输入与输出:在公共多晶硅栅极上打接触孔,并用Metal1引出一段导线作为输入端口(A)。在PMOS与NMOS有源区相邻的区域(即两管的漏极交汇处),绘制接触孔,并用Metal1连接起来,形成输出端口(Y)。

- 添加N阱(N-Well):PMOS管需要制作在N阱中。使用“NWell”层绘制一个矩形,完全包围PMOS的有源区及其周边区域,并确保与NMOS区域有足够间隔。

- 添加引脚标识(Pin):使用“Pin”层或文本工具,为金属连线上的输入(A)、输出(Y)、电源(VDD)和地(VSS)添加清晰的标签,这些标签将在后续的电路提取与验证中使用。

四、设计规则检查(DRC)

完成图形绘制后,必须运行设计规则检查。在Virtuoso中调用DRC工具,选择对应的工艺规则文件。DRC工具会自动检查版图中所有几何图形的最小宽度、最小间距、包围、延伸等规则是否违反。根据报告的错误与警告,逐一修改版图,直至通过所有检查(DRC Clean)。这是保证芯片能够被成功制造的基础。

五、版图与电路图一致性检查(LVS)

LVS验证是确保物理版图与原始逻辑电路图在电气连接上完全一致的关键步骤。

- 首先需要有一个正确的反相器电路图(Schematic)。

- 在LVS工具中,设置版图网表提取和电路图网表提取的路径。

- 运行LVS,工具会从版图中提取出器件(两个MOS管)及其连接关系,并与电路图进行比对。

- 如果LVS通过(Netlists match),表明版图连接正确。如果失败,需根据报告仔细排查是器件类型、尺寸不符,还是连接关系(如短路、开路)有误。

六、后仿真考虑与完成

通过DRC和LVS后,一个可制造且连接正确的反相器版图即告完成。为了评估其性能,可以进行寄生参数提取(如使用RCX工具),生成包含寄生电阻电容的网表,并返回到仿真环境(如Spectre)中进行后仿真,观察其瞬态响应、延迟和功耗,并与前仿真结果对比,以评估版图引入的寄生效应影响。

通过这个简单的反相器版图设计实践,我们走完了从图形绘制、设计规则遵守到电气验证的完整版图设计子流程。它深刻体现了版图设计不仅是“画画”,更是对工艺规则的严格遵守、对电气连接的精确实现以及对电路性能的物理保障。掌握这一基础单元的设计,为进一步学习更复杂的组合逻辑(如与非门、或非门)和时序逻辑(如触发器)的版图设计打下了坚实的基础。

如若转载,请注明出处:http://www.jisuyijian.com/product/63.html

更新时间:2026-04-14 15:13:41