中规模集成电路功能测试仪的设计与应用

集成电路作为现代电子技术的核心,其可靠性直接关系到整个系统的性能。随着中规模集成电路(MSI)在通信、计算机、工业控制等领域的广泛应用,对其功能与性能进行快速、准确的测试变得至关重要。因此,设计一款高效、稳定且易于操作的中规模集成电路功能测试仪,具有重要的工程价值和现实意义。

一、 中规模集成电路功能测试仪的设计目标与原则

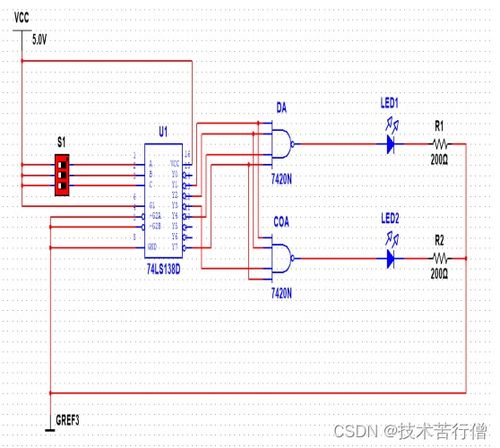

设计一款实用的MSI功能测试仪,首要目标是实现测试的自动化与高覆盖率。它应能对常见的MSI芯片,如计数器(如74LS161)、译码器(如74LS138)、寄存器(如74LS194)、数据选择器(如74LS153)等进行逻辑功能的完整验证。设计需遵循以下原则:

- 通用性与可扩展性:测试仪应具备灵活的接口和可编程的测试向量生成能力,以适应不同引脚数和逻辑功能的芯片。

- 高精度与可靠性:测试信号(电平、时序)必须精确,测试结果判定要准确可靠,避免误判和漏判。

- 操作简便与高效:提供友好的人机交互界面(如LCD显示、键盘输入),测试流程应快速,便于生产线或实验室使用。

- 成本可控:在满足性能要求的前提下,优化硬件设计,控制整体成本。

二、 系统总体架构设计

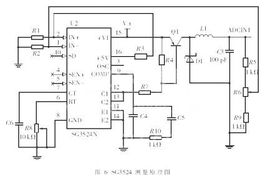

一个典型的MSI功能测试仪通常采用“核心控制器+可编程信号模块+适配接口+结果分析”的架构。

- 核心控制器:通常采用高性能微控制器(如ARM Cortex-M系列)或FPGA作为系统大脑。MCU方案成本低、控制灵活,适合逻辑相对固定的测试;FPGA方案时序控制精确、并行处理能力强,适合高速或复杂时序的测试。控制器负责执行测试流程、生成控制指令、处理人机交互和分析测试结果。

- 可编程信号模块:

- 测试向量生成单元:根据待测芯片(DUT)的真值表或功能表,在控制器管理下产生所需的输入信号序列(测试激励)。这些数据可预先存储在存储器中,或通过算法实时生成。

- 精密电源与电平转换:为DUT提供稳定、精确的VCC和GND,并确保MCU/FPGA的I/O电平(如3.3V)能与DUT的电平(如5V TTL)正确兼容。

- 时序与时钟电路:产生测试所需的精确时钟信号和各类控制时序。

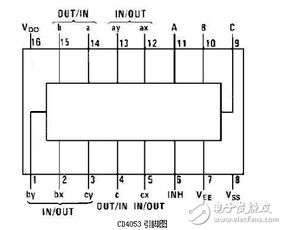

- 适配接口(DUT Socket):这是连接测试仪与待测芯片的物理桥梁。设计需考虑多芯片兼容性,通常采用“通用母座+专用适配板”的方式。适配板上包含必要的上拉/下拉电阻、信号缓冲和引脚映射电路。

- 响应采集与比较单元:实时采集DUT的输出引脚响应,并将其与预存的“期望响应”(黄金标准)进行比较。比较器电路或软件算法需考虑建立时间和保持时间,以确保采样准确。

- 人机交互与通信接口:包括键盘、LCD或触摸屏,用于型号选择、测试启动、结果显示(如“PASS/FAIL”、故障引脚信息)。同时可集成USB、RS232或以太网接口,用于测试程序更新、数据上传和远程控制。

三、 关键硬件电路设计考量

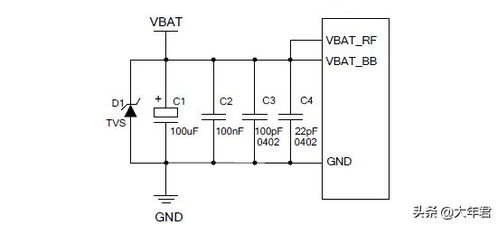

- 信号完整性:PCB布局布线时,需注意电源去耦、信号阻抗匹配、减少串扰,尤其对于高速测试信号,必要时应采用差分传输或屏蔽。

- 过流与静电保护:在接口电路设计上,需加入限流电阻和TVS管等保护元件,防止因芯片插反、短路或静电导致测试仪损坏。

- 驱动与负载能力:测试仪的驱动电路需能提供足够的电流以驱动DUT的输入引脚;其采集电路需具有高输入阻抗,以避免对DUT输出造成过重负载。

四、 软件与测试流程设计

软件是测试仪的“灵魂”,其核心是测试程序库和测试执行引擎。

- 测试程序开发:为每一类MSI芯片开发对应的测试向量集和时序控制流程。这些程序可以基于芯片数据手册,通过图形化配置或脚本语言生成。

- 测试执行流程:上电自检 -> 用户选择芯片型号 -> 系统自动加载对应测试程序 -> 通过适配接口连接DUT -> 施加电源 -> 按序施加测试激励并采集响应 -> 与预期结果逐拍比较 -> 生成并显示测试报告。

- 故障诊断:对于测试失败的芯片,软件应能定位到具体失效的功能点或引脚,提供初步的诊断信息,辅助维修与品控分析。

五、 与展望

中规模集成电路功能测试仪的设计是一个涉及数字电路、微电子、嵌入式软件和精密测量的综合性工程。一个优秀的设计需要在硬件精度、软件智能和用户体验之间取得平衡。随着集成电路向更高集成度、更低电压和更高速度发展,未来的测试仪设计将更加依赖FPGA和智能算法,并向模块化、平台化方向发展,以更灵活地应对日益复杂的测试需求。与计算机辅助设计(CAD)和自动化测试设备(ATE)系统的数据集成,也将是提升测试效率的重要方向。

如若转载,请注明出处:http://www.jisuyijian.com/product/80.html

更新时间:2026-04-14 11:20:22