产品接口篇 设计可靠的控制电路,接口电路可靠性在集成电路设计中的关键作用

在集成电路(IC)设计的广阔领域中,控制电路的设计与实现是决定产品功能、性能乃至成败的核心环节。一个卓越的控制逻辑若无法与外部世界安全、稳定、高效地“对话”,其价值将大打折扣。因此,接口电路的可靠性设计,已成为现代集成电路,尤其是面向工业、汽车、通信及消费电子等复杂应用产品设计中不可或缺的基石。本文将探讨在集成电路设计框架下,如何构建高可靠性的接口电路,以确保整个控制系统的稳健运行。

一、接口电路:系统连接的“咽喉要道”

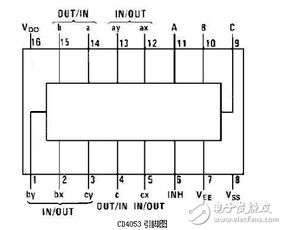

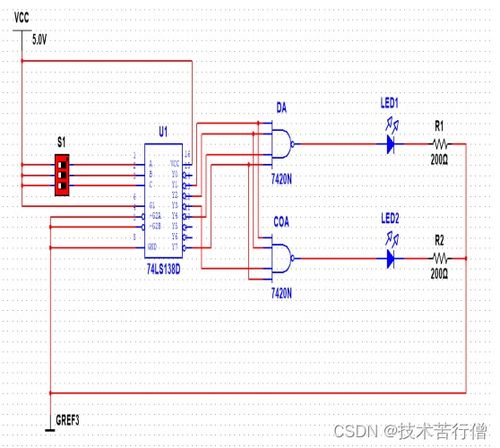

接口电路是芯片内部核心逻辑(如CPU、DSP、定制逻辑)与外部器件、总线、传感器、执行器或通信链路之间的桥梁。它负责完成电平转换、信号驱动、时序同步、协议处理、噪声隔离及保护等关键功能。无论是简单的GPIO(通用输入输出),还是复杂的PCIe、USB、DDR内存接口或车载网络(如CAN、LIN),其可靠性直接决定了:

- 数据完整性:信号在传输过程中是否产生误码。

- 时序稳定性:关键建立/保持时间能否在各类工况下得到满足。

- 系统鲁棒性:能否抵御外部噪声、静电放电(ESD)、电气过载(EOS)等干扰与损害。

- 长期耐久性:在温度循环、电压波动、老化等应力下能否持续正常工作。

二、可靠性设计的核心挑战与设计原则

在IC设计层面,提升接口电路可靠性需直面并解决以下挑战:

1. 信号完整性(SI)与电源完整性(PI)

- 挑战:高速信号下的反射、串扰、衰减;电源网络噪声导致信号电平抖动。

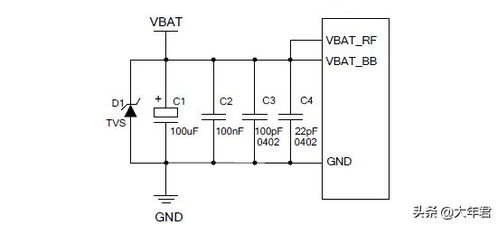

- 设计原则:采用阻抗匹配设计(如片上终端电阻);优化布局布线,减少并行长线以降低串扰;设计稳健的电源分配网络(PDN)和去耦电路;对关键时序路径进行严格约束和仿真。

2. 静电放电(ESD)与闩锁(Latch-up)防护

- 挑战:人体或机器模型ESD可能瞬间损坏脆弱的输入级晶体管;寄生PNPN结构在干扰下触发闩锁,导致大电流烧毁。

- 设计原则:在所有引脚集成符合JEDEC标准(如HBM, CDM)的ESD保护结构(如二极管、GGNMOS、SCR);采用保护环(Guard Ring)、深N阱等工艺和版图技术有效抑制闩锁效应。

3. 电压容限与热插拔支持

- 挑战:接口需兼容不同供电系统的器件(如1.8V与3.3V逻辑互连);支持带电插拔而不损坏。

- 设计原则:设计宽电压容限的输入接收器(如施密特触发器、带电平偏移的电路);使用背对背MOSFET、缓启动电路等实现热插拔控制,限制浪涌电流。

4. 电磁兼容性(EMC)

- 挑战:接口既是噪声发射源,也是敏感接收器,需满足相关EMC法规。

- 设计原则:优化驱动器的压摆率控制以减少高频辐射;采用差分信号传输(如LVDS)增强抗共模噪声能力;在版图上隔离数字噪声对模拟/射频部分的影响。

5. 故障安全与冗余设计

- 挑战:在系统局部故障或极端条件下,接口行为需可预测,避免导致系统崩溃。

- 设计原则:内置上拉/下拉电阻确保未连接时处于确定状态;对关键控制信号实现“看门狗”或超时机制;在高端应用中,可采用双通道冗余接口设计。

三、从设计到验证的可靠性保障流程

可靠的接口电路非一蹴而就,必须融入完整的IC设计流程:

- 规范制定:明确接口的电气特性(电压、电流、时序)、协议标准、可靠性目标(ESD等级、工作温度范围、寿命)。

- 架构与电路设计:根据规范选择适当的接口类型(推挽、开漏、差分),设计核心电路模块(驱动器、接收器、电平转换器、ESD单元),并进行前仿真。

- 版图实现:这是可靠性物理实现的关键。需严格遵守设计规则(DRC),实施静电防护、闩锁防护的版图布局,考虑电流密度、电迁移(EM)规则,并优化信号与电源的走线。

- 后仿真与验证:提取寄生参数(PEX)后,进行包含SI/PI效应的后仿真,验证时序、噪声容限和ESD性能。进行形式验证以确保逻辑功能正确。

- 工艺角与蒙特卡洛分析:在工艺、电压、温度(PVT)变化以及器件参数离散性(蒙特卡洛分析)下,验证接口性能的鲁棒性。

- 系统级协同仿真:在可能的情况下,与PCB模型进行协同仿真,评估芯片-封装-板级的系统级互连性能。

四、

在“产品接口篇”的语境下,设计可靠的控制电路,接口电路的可靠性不是可选项,而是强制项。它要求集成电路设计师不仅精通晶体管级电路设计,还需具备系统级视角,深刻理解信号完整性、电源管理、防护机制与制造工艺之间的复杂相互作用。通过将可靠性设计原则贯穿于从架构到版图的每一个环节,并辅以严谨的仿真与验证,才能锻造出在真实、严苛环境中稳定服役的集成电路产品,从而为最终电子系统的卓越性能与长久寿命奠定坚实基础。

如若转载,请注明出处:http://www.jisuyijian.com/product/74.html

更新时间:2026-05-12 17:19:48