集成电路中低功耗乘法器的实现与设计

随着移动通信、物联网、可穿戴设备等领域的飞速发展,对集成电路的性能和功耗提出了更为苛刻的要求。乘法器作为数字信号处理、图像处理、人工智能加速器等核心运算单元中的关键部件,其功耗往往占据整个系统功耗的相当大比重。因此,研究与设计高性能、低功耗的乘法器,对于实现高效能的片上系统(SoC)和延长便携式设备的电池续航时间具有至关重要的意义。

一、低功耗设计挑战与设计层次

在深亚微米乃至纳米工艺节点下,集成电路的功耗主要由动态功耗、静态功耗和短路功耗三部分组成。对于乘法器这类频繁进行数据运算的模块,动态功耗是其功耗的主要来源。低功耗设计是一个系统工程,需要从系统架构、算法、电路结构乃至物理版图等多个层面进行协同优化。

- 系统与算法级:在最高抽象层次,可以通过选择合适的算法来减少乘法操作的次数或复杂度。例如,采用分布式算法、Booth编码算法等,可以从根本上减少部分积的生成数量,从而降低后续加法树压缩的规模和功耗。

- 架构与RTL级:此层级的设计包括选择适合的乘法器结构(如阵列乘法器、树形乘法器)、采用门控时钟技术、操作数隔离、动态电压频率调节(DVFS)等。门控时钟可以精准地关闭乘法器在空闲周期内的时钟网络,消除不必要的时钟翻转功耗。

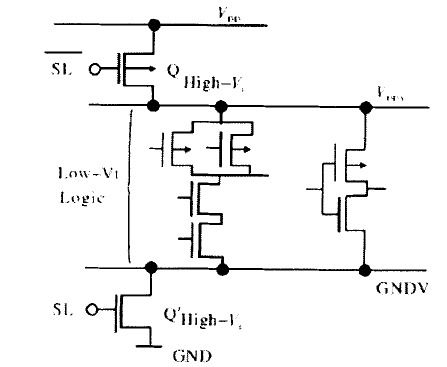

- 电路与逻辑级:采用低功耗逻辑单元,如传输门逻辑、多米诺逻辑的优化变种,或者使用多阈值电压(Multi-Vt)库,在关键路径使用低阈值电压单元保证速度,在非关键路径使用高阈值电压单元降低漏电。优化晶体管尺寸(尺寸缩放)也是常用手段。

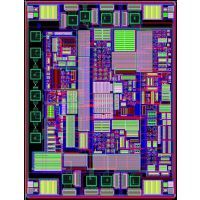

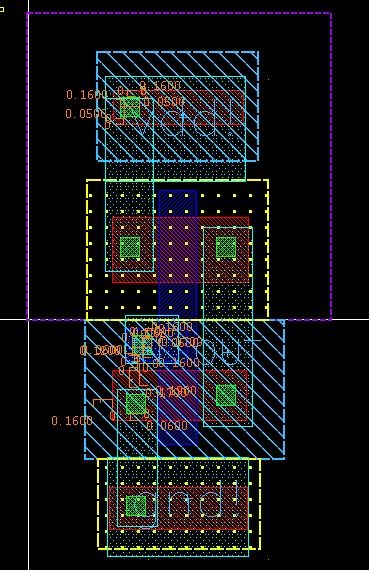

- 物理版图级:通过精细的布局布线,减少关键长互连线的电容,从而降低其翻转功耗。采用电源门控技术,在乘法器长时间不工作时,可以切断其电源供应,近乎消除静态功耗。

二、关键实现技术与结构

- Booth编码算法:这是一种广泛用于减少部分积数量的算法。通过将乘数重编码为有符号数字,可以将连续“1”的序列转换为更少的运算操作(如“+M, 0, -M”),典型情况下能将部分积数量减少近一半,显著降低了部分积累加阵列的规模和功耗。改进的基-4 Booth编码是其高效实现之一。

- Wallace树与压缩树结构:部分积生成后,需要将其压缩求和。Wallace树采用全加器(3:2压缩器)和半加器以树形结构快速压缩部分积,其结构不规则但速度快。为了平衡速度与规整性,4-2压缩器被广泛用于构建规整的压缩树(如Dadda树),它在保持高速的更利于自动布局布线,并能减少中间节点的开关活动性。

- 近似计算技术:在允许一定计算误差的应用场景(如图像处理、机器学习推理),近似乘法器可以大幅降低功耗。通过截断不重要的部分积、简化压缩树结构或使用近似的加法器单元,可以在可接受的精度损失下,实现功耗和面积的显著优化。

- 异步电路设计:与全局同步时钟驱动的电路不同,异步乘法器采用握手协议进行局部通信和数据传递。它消除了全局时钟树带来的巨大功耗,并且仅在有数据活动时消耗能量,无空转功耗。虽然设计复杂,但在极致低功耗场景下潜力巨大。

三、设计流程与权衡

设计一个低功耗乘法器并非单纯追求功耗最低,而需要在功耗(Power)、性能(Performance)、面积(Area)和精度(Accuracy) 之间取得最佳平衡,即所谓的PPAA权衡。

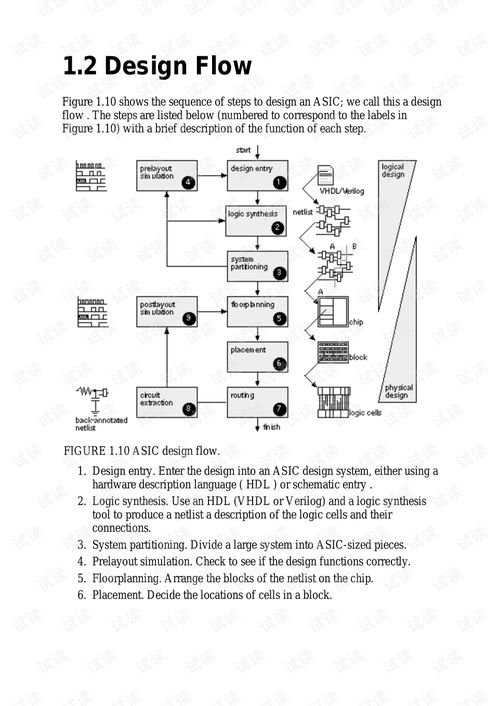

设计流程通常从系统需求分析开始,确定所需的精度(如整型、浮点型、位宽)和性能指标(如最大工作频率、吞吐率)。然后,在算法和架构层面进行探索,选择合适的基础算法和整体结构。接着,使用硬件描述语言(如Verilog/VHDL)进行RTL实现,并集成门控时钟等低功耗设计意图。之后,通过逻辑综合工具,结合多阈值电压库和时钟门控插入策略,生成门级网表。在物理实现阶段,利用布局布线工具进行精细优化,并可能引入电源门控。需要通过仿真和功耗分析工具(如PrimeTime PX)在不同向量下进行严格的功耗验证。

四、未来展望

面向低功耗乘法器的设计将面临工艺持续微缩带来的量子效应、漏电问题加剧以及新兴计算范式的挑战。一方面,新器件(如FinFET, GAA FET)和新材料为电路设计带来了新的机遇;另一方面,存内计算、模拟计算等非冯·诺依曼架构试图从根本上打破“内存墙”和功耗限制,将乘法运算与存储结合,这为超低功耗乘加运算开辟了全新的技术路径。面向特定领域(如AI)的定制化近似乘法器也将持续成为研究热点。

集成电路中低功耗乘法器的设计与实现是一个多层级、多技术融合的复杂课题。工程师必须深入理解从算法到物理的整个设计链,灵活运用各种低功耗技术,才能在满足严苛性能要求的打造出能效比卓越的运算核心单元,推动电子系统向着更智能、更绿色的方向发展。

如若转载,请注明出处:http://www.jisuyijian.com/product/60.html

更新时间:2026-04-14 13:23:55